# Construction and analysis of a 3-Level Diode Clamped 3-Phase Multilevel Inverter using Simulink/MATLAB

Dr. Manjesh, Associate Professor, Department of Electronic Science,

Bangalore University, Bangalore, India.

**Abstract**: The reduction of harmonics are the major challenging work in industry, most of the industries use high torque load induction motors. It is very essential to monitor the life time of the induction motor if the motors are running long time [1]. In this paper the harmonic analysis of the three phase three level diode clamped multilevel inverter drive is constructed and studied for its total harmonic distortion using simulink/Matlab, the work is validated with the results.

Index: THD, harmonics, inverter, PWM.

## I. INTRODUCTION

The various inverters are used to drive the induction motors in industries due to many advantageous. The multilevel inverter is one which is used to drive the induction motors in various applications [2], the advantage of using these inverters are low harmonic content [3] and the output of the inverter is constructed to approximate sinusoidal voltage, which intern reduces the harmonic content at the output of the inverter. the harmonics create major problems in the motors, these harmonics doesn't contribute any additional voltage or current it is simply dissipated as heat in the windings of the induction motor [4], therefore, the main target of the research work is to minimize the harmonic content at the output of the inverter, hence various inverters studied and used to drive the induction motor. In this research work a simulation work has been done to obtain the output voltage at the output of the 3-Pase, 3-Level Multilevel Inverter [6].

The research work describes the working of three phase three level Diode Clamped Multilevel Inverter (DCMI) drive with twelve switches. Simulink/MATLAB simulation software is used to simulate the three phase three level DCMI drive. The drive is also constructed experimentally for future study of temperature analysis of induction motor. The harmonics and THD are analysed at the output of the inverter, power analyzer WT-500 is used to measure harmonics and total harmonic distortion (THD). The motor is placed with thermocouples at different parts and the temperature is measured with temperature module kit, the system is connected to a computer. The motor is operated for low input v/f profiles ie., frequencies of 1Hz to 10Hz, the temperature, harmonics and THD are recorded, the results are used to compare the predicted temperature obtained by thermal model. Temperature obtained by traditional inverter drive (TID) fis also compared.

# II. WORKING PRINCIPLE OF DCMI

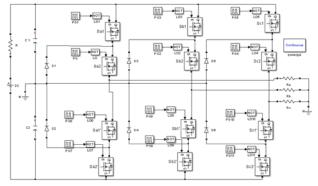

Buck The 3-level Diode Clamped Multilevel Inverter (DCMI) drive is constructed with twelve switches as shown in figure 1.1. The control signals are used to drive the MOSFET's through a drive circuit, The MOSFET's are turned on with phase difference of  $120^{\circ}$  between each phase. The switch  $S_{b2}$  is switched on with phase delay of  $120^{\circ}$  with respect to  $S_{a2}$  and  $S_{c2}$  is switched on with phase delay of  $120^{\circ}$  with respect to  $S_{b2}$ . The switches  $S_{a1}$ ,  $S_{b1}$  and  $S_{c1}$  are turned on with a delay of  $20^{\circ}$  in each phase with  $S_{a2}$ ,  $S_{b2}$  and  $S_{c2}$  respectively, the switches are ON for  $140^{\circ}$  duration. The switches  $S_{a2}$ ,  $S_{b2}$  and  $S_{c2}$  conduct for a duration of  $170^{\circ}$  instead of  $180^{\circ}$ , this delay is given for the switches to turn on or off without shorting the leg. The classification of switches is done as upper switches and lower switches. The switches  $S_{a1}$ ,  $S_{a2}$ ,  $S_{b1}$ ,  $S_{b2}$ ,  $S_{c1}$  and  $S_{c2}$  are upper switches and  $S_{a1}$ ,  $S_{a2}$ ,  $S_{b1}$ ,  $S_{b2}$ ,  $S_{c1}$  and  $S_{c2}$  with respect to their upper switches -  $S_{a1}$ ,  $S_{a2}$ ,  $S_{b1}$ ,  $S_{b2}$ ,  $S_{c1}$  and  $S_{c2}$  with respect to their upper switches -  $S_{a1}$ ,  $S_{a2}$ ,  $S_{b1}$ ,  $S_{b2}$ ,  $S_{c1}$  and  $S_{c2}$  with respect to their upper switches -  $S_{a1}$ ,  $S_{a2}$ ,  $S_{b1}$ ,  $S_{b2}$ ,  $S_{c1}$  and  $S_{c2}$ . This switching of the MOSFET's are used to synthesise the inverter output approximately sinusoidal output voltage pattern, hence the patterns are switched with two sets of switches from upper group are ON and one set of switches from lower group is ON or two sets of switches from lower group are ON and one set of switches from upper group is ON.

The Figure 1.1 shows three phase multilevel inverter drive with 3-phase load. The simulation software simulink/MATLAB is used to simulate the three level diode clamped multilevel inverter drive. The circuit in figure 1.1 is used for simulation [4]. The simulation of 3-level DCMI (Diode Clamped Multilevel Inverter) drive is carried out to observe the approximate inverter output to drive the 3 phase induction motor, THD and harmonics are recorded[5].

Figure 1.1. Circuit layout of 3 phase 3-level DCMI drive using simulation

The Figure 1.1 shows three phase multilevel inverter drive with 3-phase load. The simulation software simulink/MATLAB is used to simulate the three level diode clamped multilevel inverter drive. The circuit in figure 1.1 is used for simulation [4]. The simulation of 3-level DCMI (Diode Clamped Multilevel Inverter) drive is carried out to observe the approximate inverter output to drive the 3 phase induction motor, THD and harmonics are recorded[5].

### III. SIMULATION RESULTS

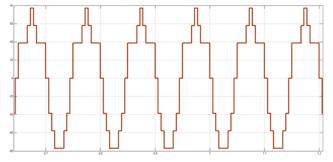

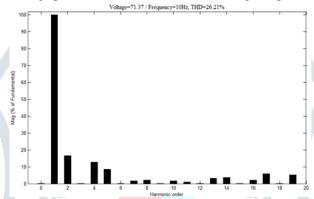

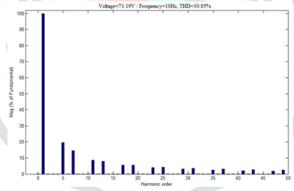

The construction and simulation of the three phase three level DCMI drive simulink/MATLAB is done with R load is as shown the figure 1.1. The MOSFET's are triggered with pulse generators (PG-PG11). The output voltage at the load for phase A is obtained as shown in figure 1.2. for the fundamental frequency of 10Hz has been consider for operation, harmonic profile for the output voltage waveform of 3-Phase, 3-Level Multilevel Inverter Drive is shown in Figure 1.3 and Figure 1.4 shows the harmonic profile of 3-Phase normal inverter drive, from the results it has been observed that THD of 3-Phase, 3-Level, Multilevel inverter drive is 26.21%, and the normal 3-Phase Inverter drive is 30.85%.

Figure 1.2. Time/voltage plot of a first Phase to Neutral voltage output waveform at load Ra

Figure.1.3. Harmonic Profile of Normal 3-Phase Inverter

Figure 1.4. Harmonic Profile for 3 level DCMI drive

# IV. CONCLUSION

The harmonic analysis of 3-Phase, 3-Level Multilevel inverter has been studied and the simulation work is carried out the output voltage at the output of the 3-Phase, 3-Level, Multilevel Inverter drive is found to be approximately sine wave therefore the harmonic content and Total Harmonic Distortion is less compared to three phase Normal Drive Inverter.

# **REFERENCES:**

- [1] K. Corzine, "Operation and design of multilevel inverters," Dev. Off. Nav. Res., no. December 2003, pp. 1–79, 2003.

- [2] S. R. Gandimeni and V. K. K, "Unified Power Quality Conditioner (UPQC)," Power Qual. Power Syst. Electr. Mach., vol. 2, no. 8, pp. 443-468, 2008.

- J. S. . and P. . Murugesan.G, "a New Multilevel Inverter Topology Using Less Number of Switches," Int. J. Eng. Sci. Technol., vol. [3] 3, no. 2, 2011.

- [4] G. Brando, A. Dannier, A. Del Pizzo, R. Rizzo, and I. Spina, "Torque derivative control in induction motor drives supplied by multilevel inverters," vol. 9, pp. 2249-2261, 2016.

- [5] A. Nordvall, "Multilevel Inverter Topology Survey Master of Science Thesis in Electric Power Engineering Division of Electric Power Engineering Multilevel Inverter Topology Survey," p. 78, 2011.

- [6] O. Bouhali, N. Rizoug, and B. Francois, "Equivalent matrix structure modelling and control of a three-phase flying capacitor multilevel inverter," IET Power Electron., vol. 7, no. 7, pp. 1787–1796, 2014.

- [7] M. Veenstra, "MULTI-LEVEL INVERTER FOR MEDIUM-VOLTAGE APPLICATIONS," vol. 2846, 2003.

- [8] 8. B. J. Rabi and R. Arumugam, "Harmonics Study and Comparison of Z-source Inverter with Traditional Inverters," Am. J. Appl. Sci., vol. 2, no. 10, pp. 1418–1426, 2005.